Développement d'un simulateur de d'ordinateur 8 bits avec une interface web

Projet personnel - Formation GymInf

Nicolas Kunz (Gymnase d'Yverdon)

nicolas.kunz@eduvaud.ch

Superviseuse : Biljana Petreska von Ritter-Zahony

Introduction

Motivations

Simulateurs existants

Conception

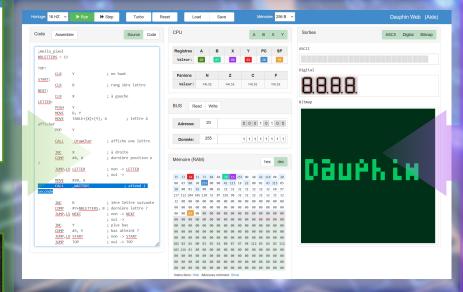

Dauphin Web

Interface

Fonctionnement

Discussion

vs. simulateur de Dauphin

Validation

**Améliorations**

Activité

Retour sur l'activité

## Motivations

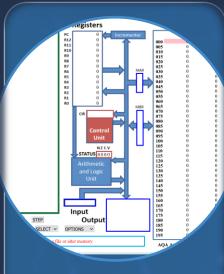

#### AQA Processor Simulator

Peter Higginson

- + Flux des données

- Vite désorientant

#### Simple 8-bit Assembler Simulator

Marco Schweighauser

- + Interface utilisateur

- Limité

AQA Processor Simulator

Peter Higginson

- + Flux des données

- Vite désorientant

Simple 8-bit

Assembler Simulator

Marco Schweighauser

- + Interface utilisateur

- Limité

AQA Processor Simulator

Peter Higginson

- + Flux des données

- Vite désorientant

Simple 8-bit

Assembler Simulator

Marco Schweighauser

- + Interface utilisateur

- Limité

Pauphin

EPSITEC

+ Fonctionnalité

- Accessibilité

Simulateur de Dauphin

COUMMANT COOT SOURCE TRANCE

Bus d'adresse

Bus d'adresse

AQA Processor Simulator

Peter Higginson

- + Flux des données

- Vite désorientant

Simple 8-bit

Assembler Simulator

Marco Schweighauser

- + Interface utilisateur

- Limité

## Conception

Simple 8-bit Assembler Simulator

Marco Schweighauser

- + Interface utilisateur

- Limité

# Conception

Simulateur de Dauphin

Simple 8-bit Assembler Simulator

# Code

Simple 8-bit Assembler Simulator

## Conception

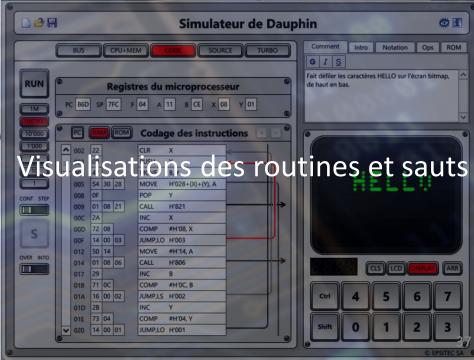

## Simulateur de Dauphin

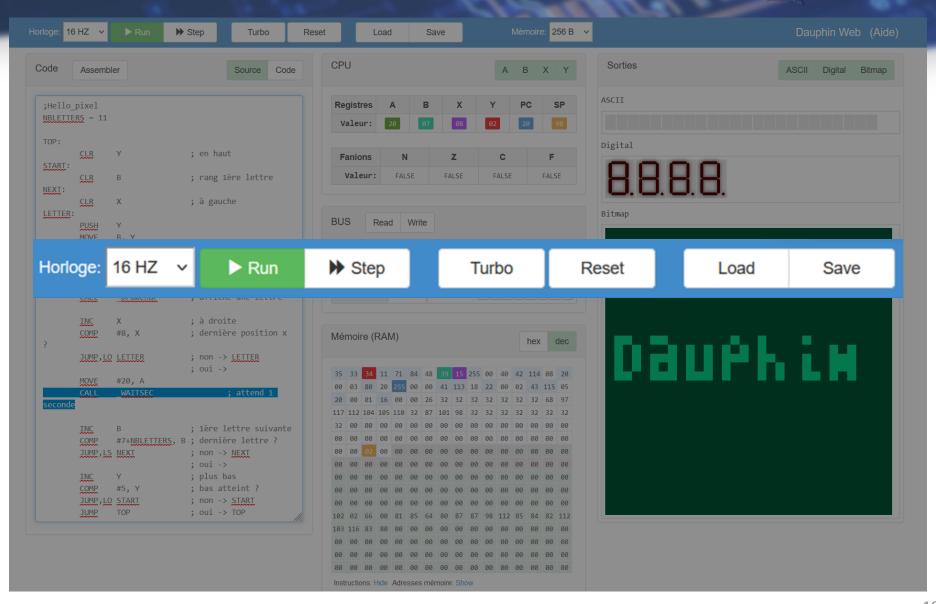

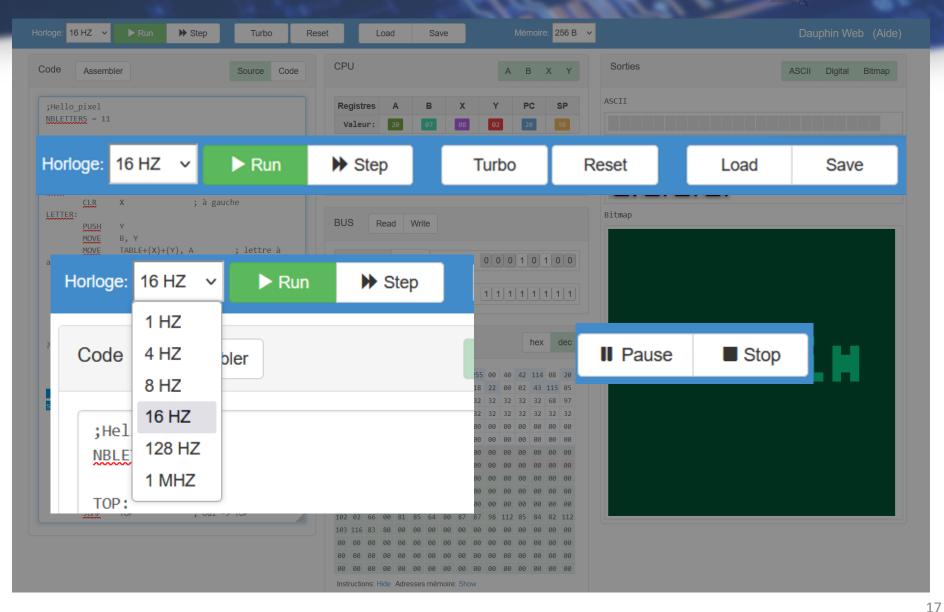

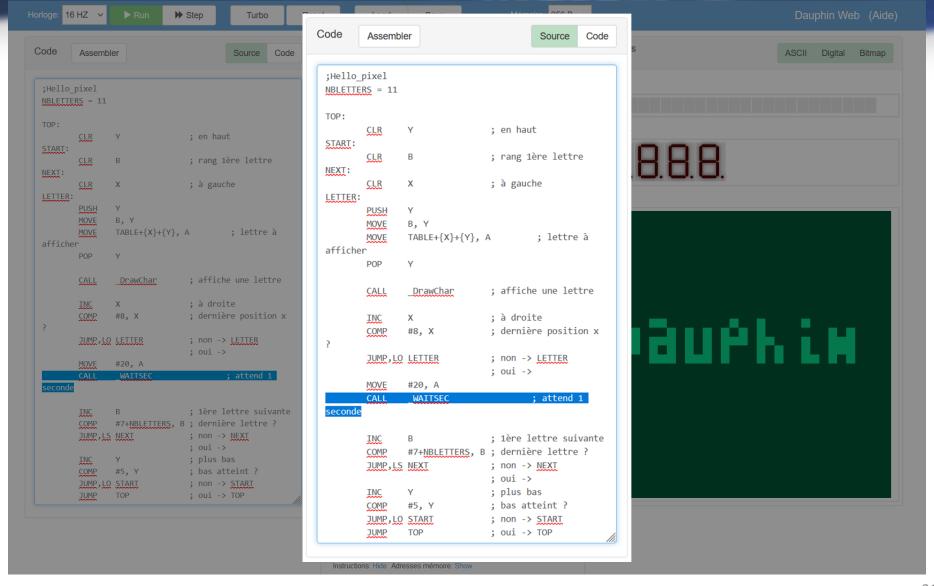

Assembleur

Turbo

#### Simulateur de

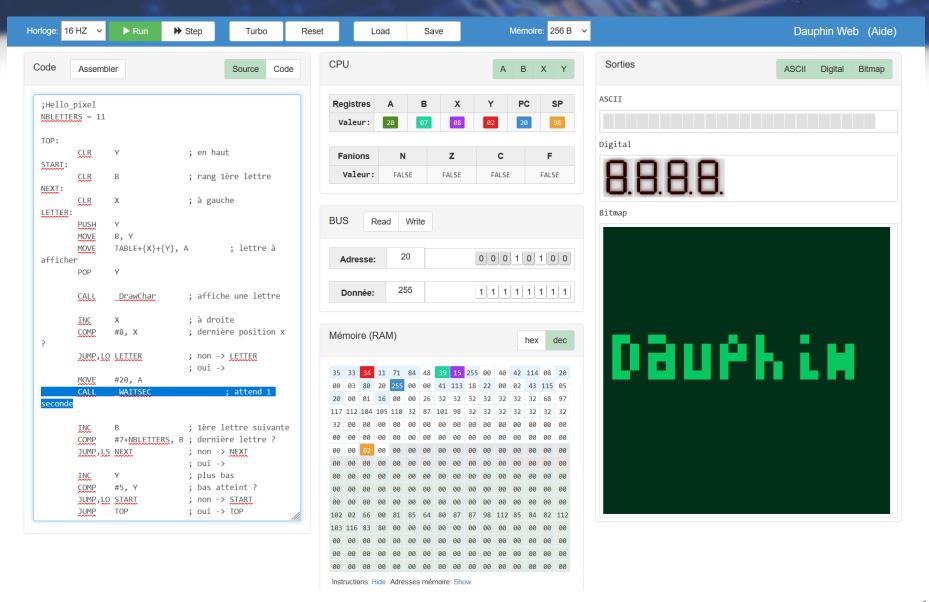

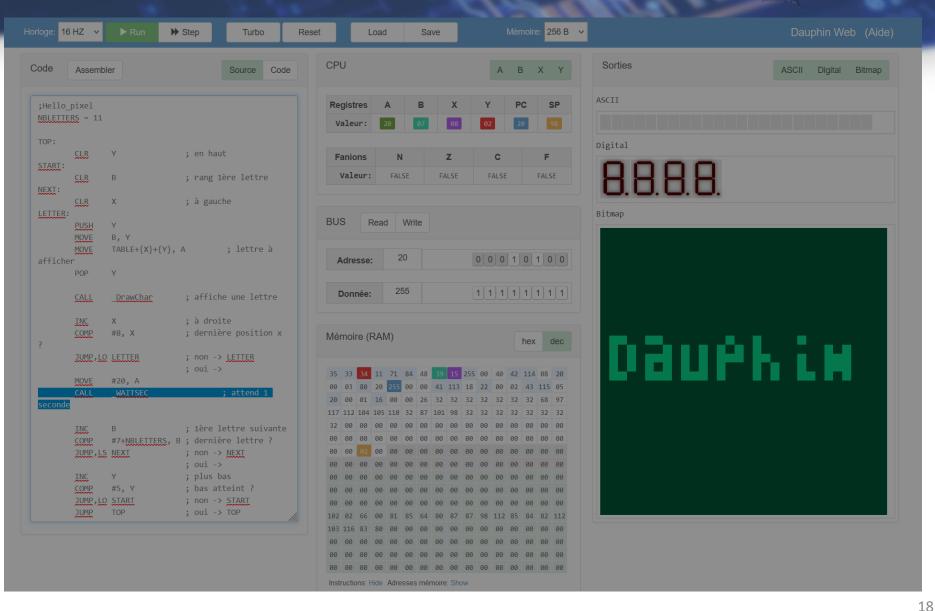

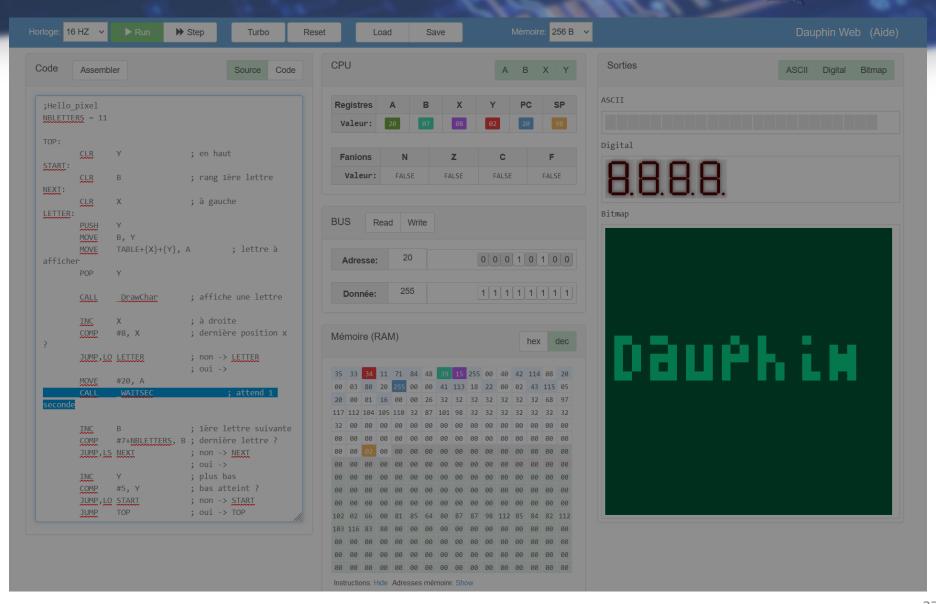

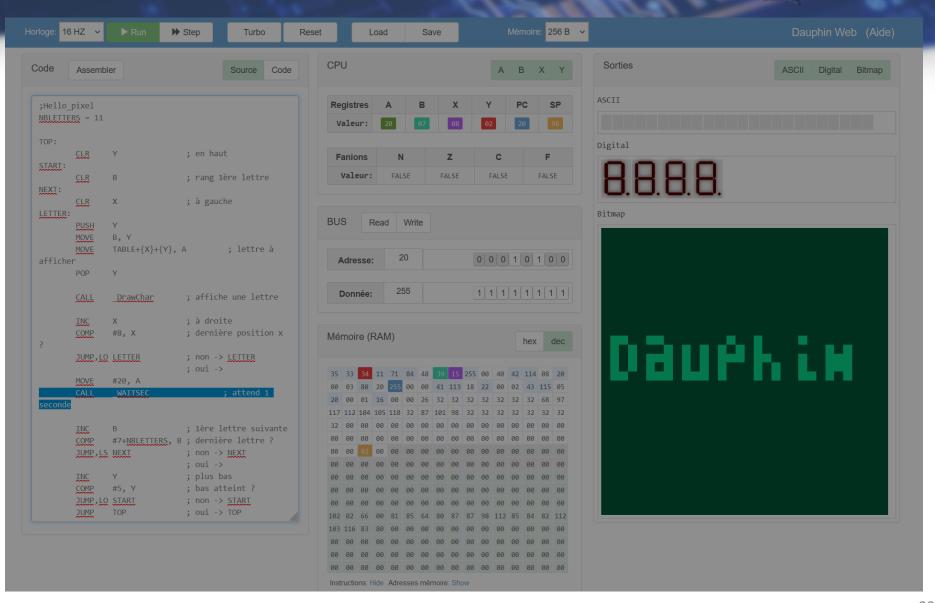

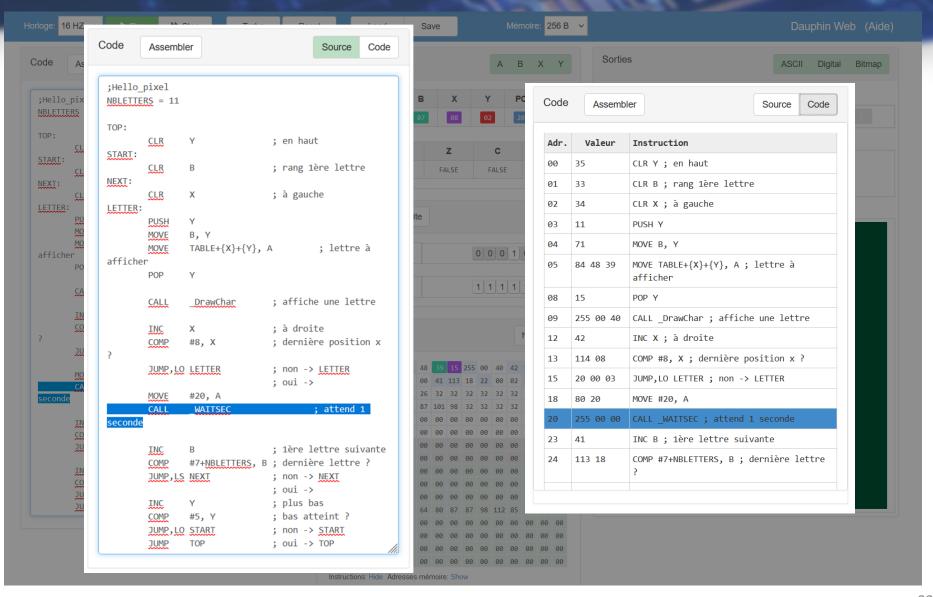

Dauphin Web (Aide)

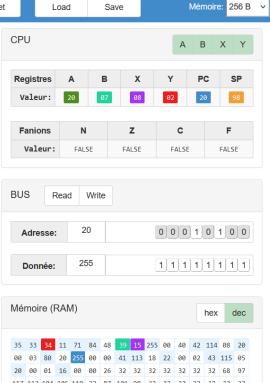

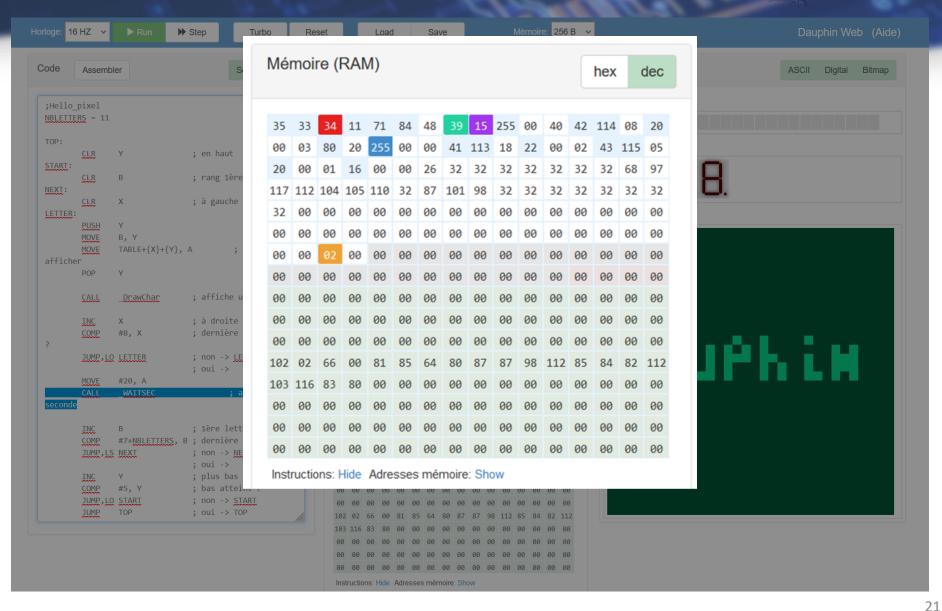

| Mémoire (RAM) |     |     |     |     |    |    |     |     |     |    |     |    | hex | (   | dec |  |

|---------------|-----|-----|-----|-----|----|----|-----|-----|-----|----|-----|----|-----|-----|-----|--|

| 35            | 33  | 34  | 11  | 71  | 84 | 48 | 39  | 15  | 255 | 00 | 40  | 42 | 114 | 08  | 20  |  |

| 00            | 03  | 80  | 20  | 255 | 00 | 00 | 41  | 113 | 18  | 22 | 00  | 02 | 43  | 115 | 05  |  |

| 20            | 00  | 01  | 16  | 00  | 00 | 26 | 32  | 32  | 32  | 32 | 32  | 32 | 32  | 68  | 97  |  |

| 117           | 112 | 104 | 105 | 110 | 32 | 87 | 101 | 98  | 32  | 32 | 32  | 32 | 32  | 32  | 32  |  |

| 32            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 02  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 102           | 02  | 66  | 00  | 81  | 85 | 64 | 80  | 87  | 87  | 98 | 112 | 85 | 84  | 82  | 112 |  |

| 103           | 116 | 83  | 80  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

| 00            | 00  | 00  | 00  | 00  | 00 | 00 | 00  | 00  | 00  | 00 | 00  | 00 | 00  | 00  | 00  |  |

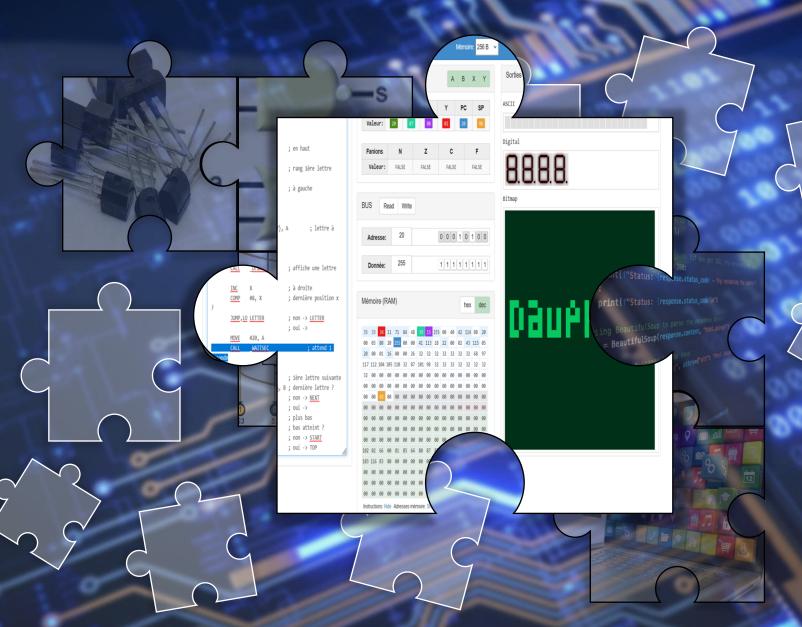

Assembler Simulator

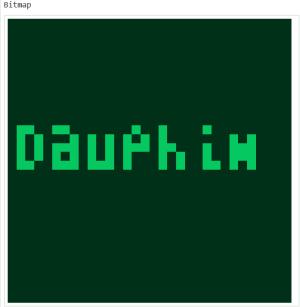

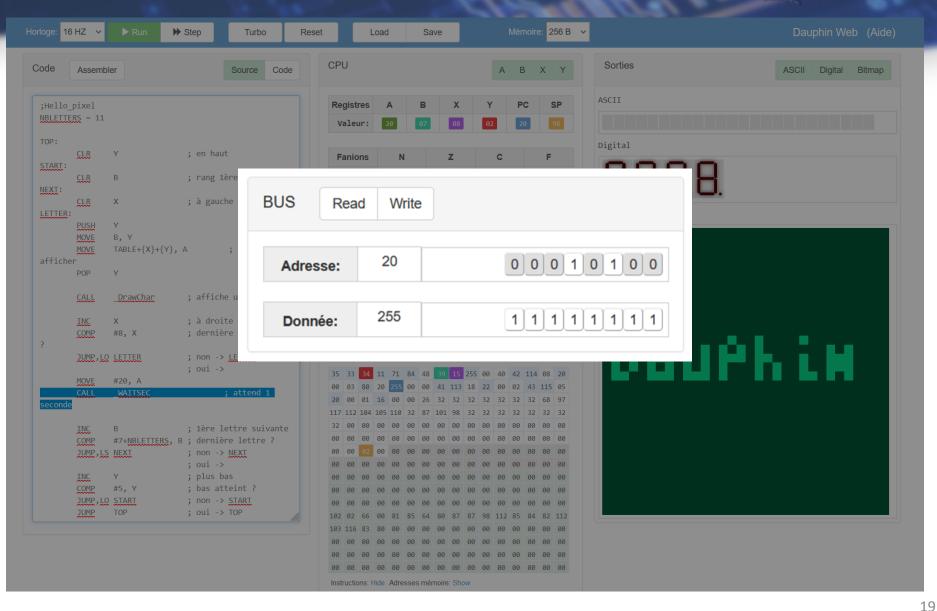

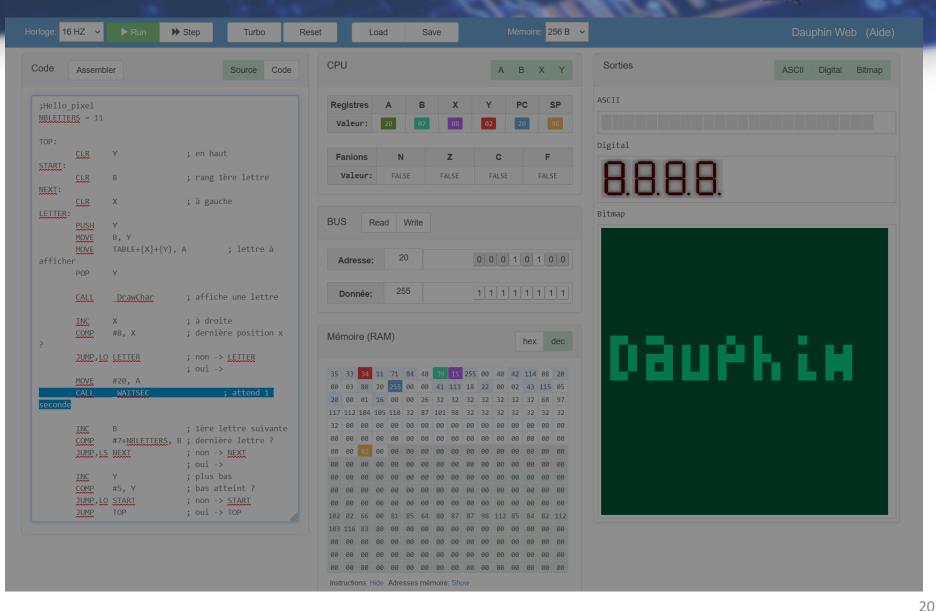

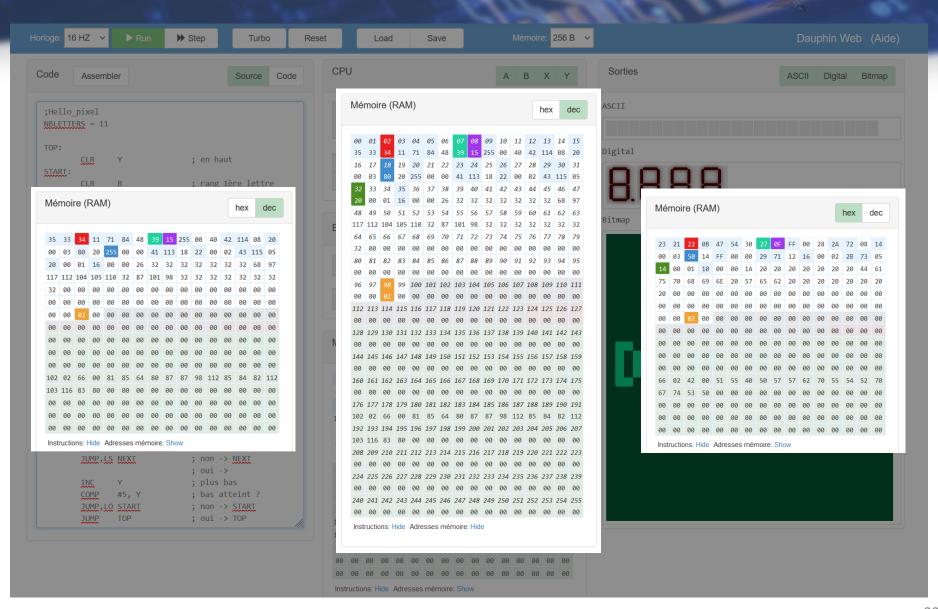

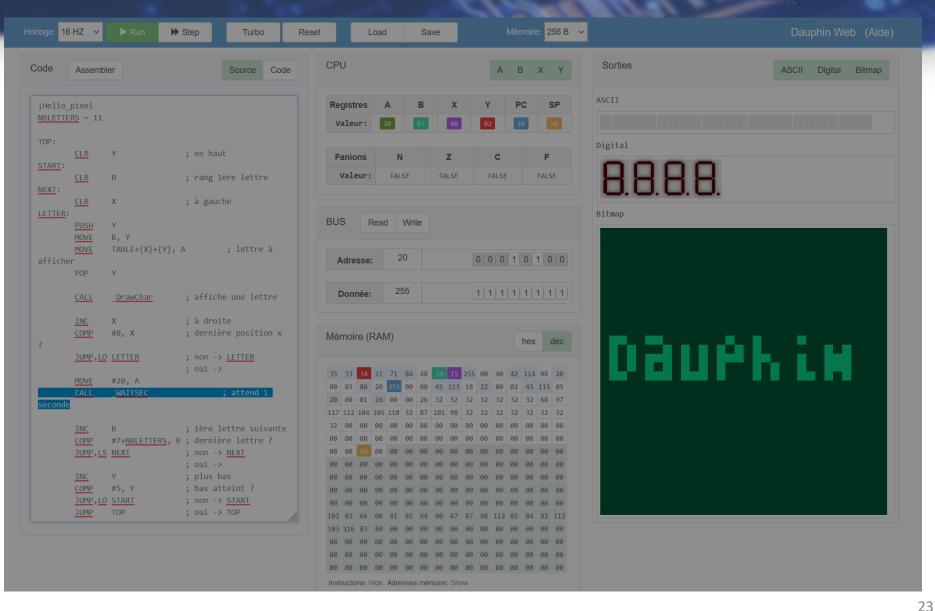

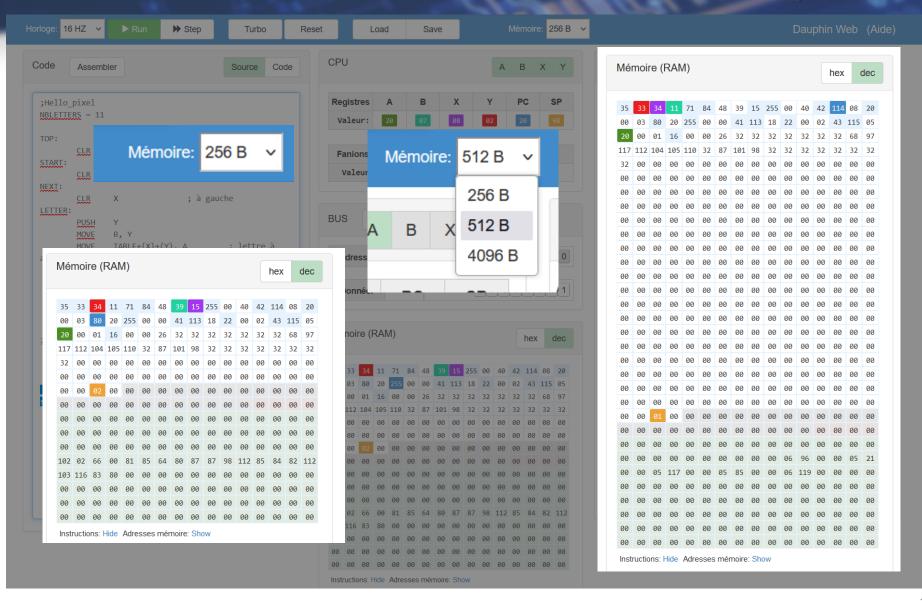

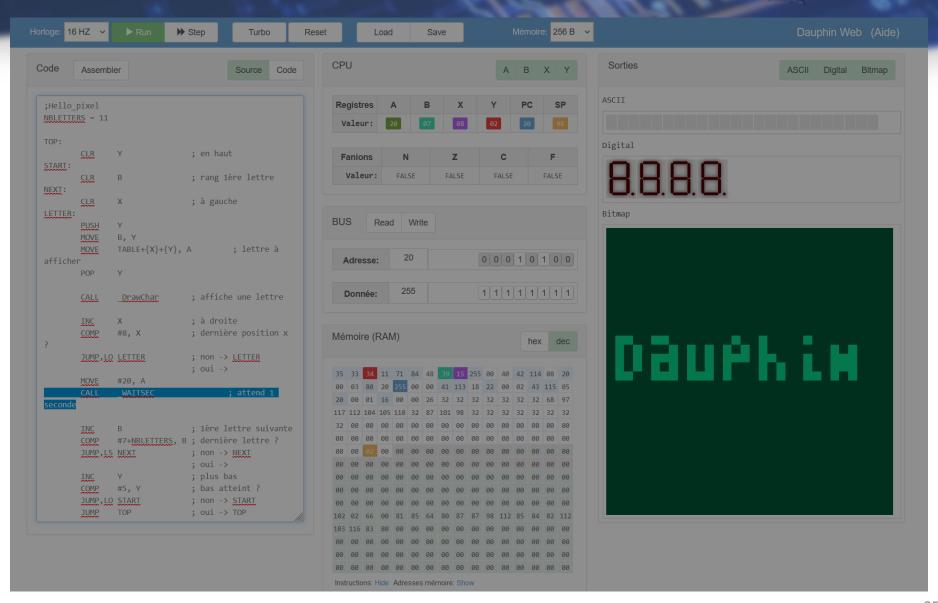

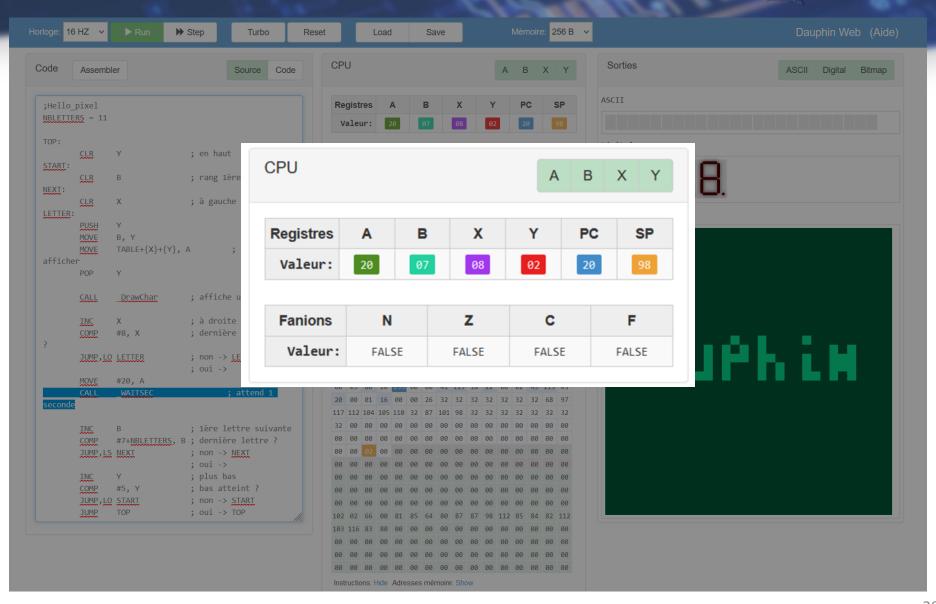

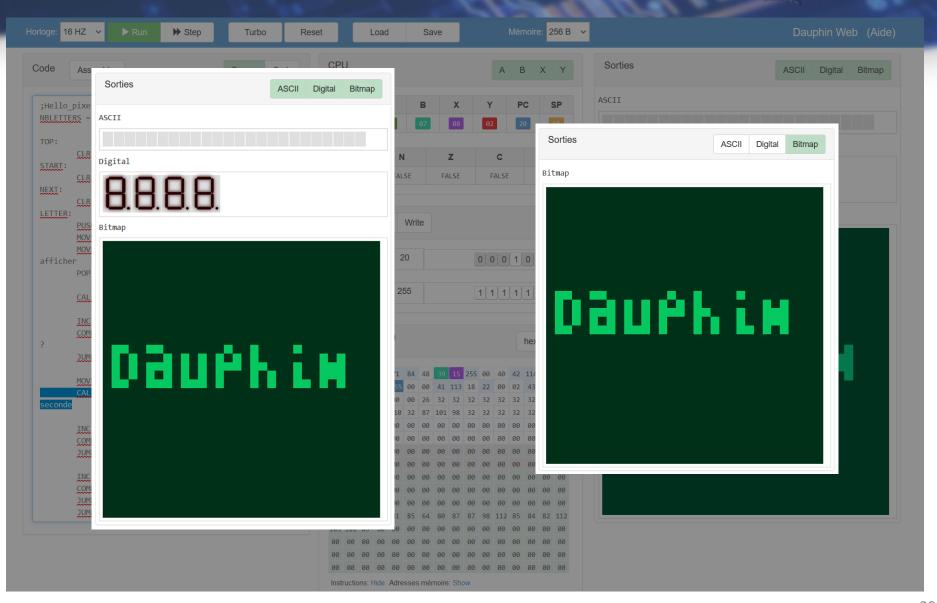

Interface Sorties ASCII Digital Bitmap Horloge: 16 HZ V → Step Turbo ASCII Code Assembler Source ASCII Digital Bitmap Digital ;Hello\_pixel 8888 NBLETTERS = 11 ; en haut START: 1.8.8. Bitmap ; rang 1ère lettre ; à gauche LETTER: В, Y TABLE+ $\{X\}+\{Y\}$ , A ; lettre à afficher POP ; affiche une lettre DrawChar ; à droite Dauphim COMP #8, X ; dernière position auphim JUMP, LO LETTER ; non -> LETTER #20, A ; attend 1 ; 1ère lettre suiva COMP #7+NBLETTERS, B; dernière lettre ; non -> NEXT COMP #5, Y ; bas atteint ? ; non -> START ; oui -> TOP Instructions: Hide Adresses mémoire: Show

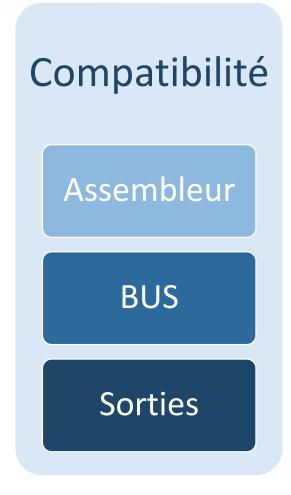

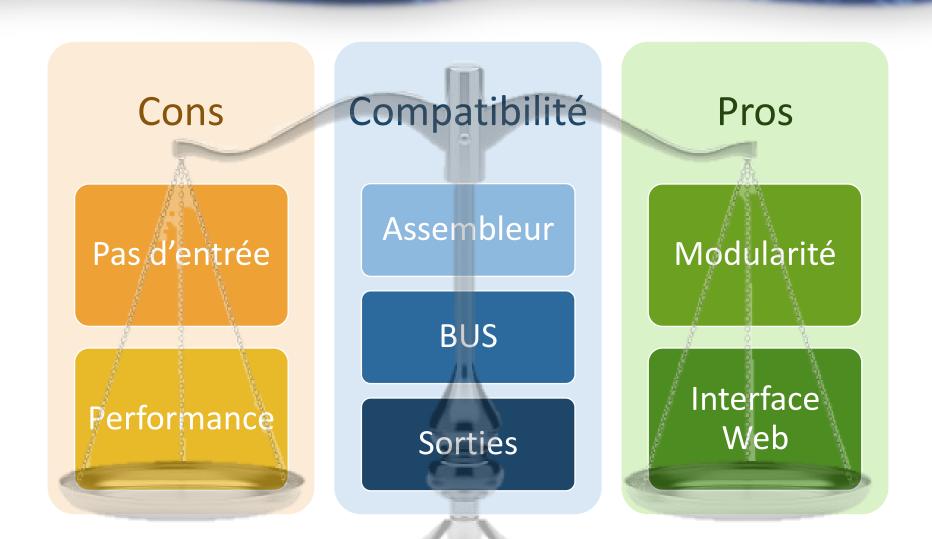

## Dauphin Web vs. Simulateur de dauphin

## Dauphin Web vs. Simulateur de dauphin

#### Validation

#### **Fonctionnement**

Tests extensifs de toutes les commandes

#### Outil pédagogique

Hérité de son ainé

## Activités

https://kunznicolas.github.io/Web Dauphin/

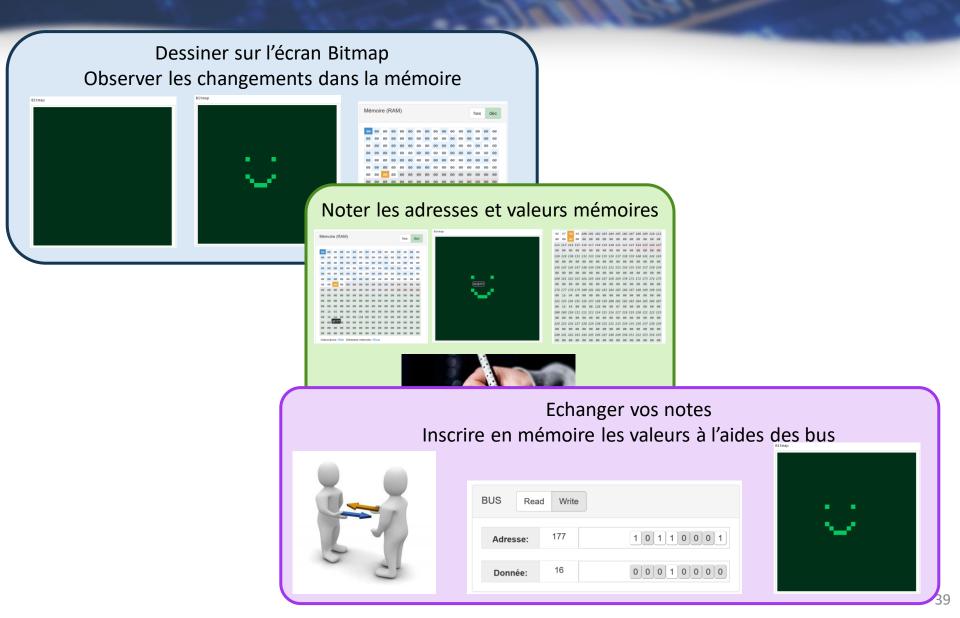

## Activité 1 – affichage / mémoire / bus

## Conclusion

Dauphin Web:

Simulateur d'ordinateur 8bits

Application web

Open-source (GitHub)

Compatible avec le simulateur de l'EPSITEC

Outils déjà établis comme atout pédagogique

Test en classe

Problème de performance

#### Remerciements

- Biljana Petreska von Ritter-Zahony (HEP Vaud)

- Jean-Philippe Pellet (HEP Vaud)

- Michel Favre (Gymnase d'Yverdon)

- Laurent Michel (Gymnase de Beaulieu)

- Pierre Arnaud (et l'EPSITEC)

- Andreas Humm (UNIFR, GymInf)

- Mélissa Nicolier et Arthur Dromard (Gymnase d'Yverdon, GymInf)

- Yohan Sanchez (Gymnase d'Yverdon, correcteur)

#### SV A/SS E/SS I

UNIVERSITÉ DE FRIBOURG UNIVERSITÄT FREIBURG